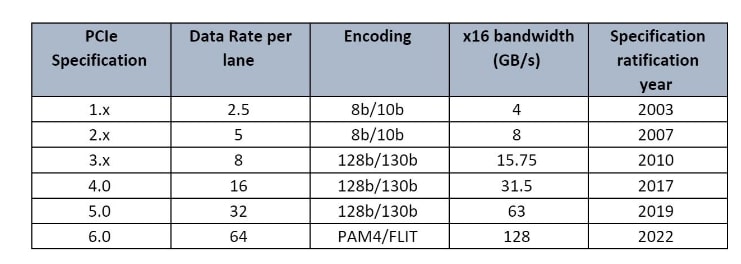

While the PCI-SIG has declared that the publication of the PCI Express® 6.0 (PCIe 6.0) specification should arrive in 2022, Rambus is currently addressing the demands of early adopters searching for the most sophisticated PCIe 6.0 IP solutions for their SoC and ASIC designs.

Related Reads: PCIe Gen 3 vs PCIe 4.0

PCIe 6.0

Ever Since PCIe 3, the data rate has doubled with each succeeding generation of the standard. PCIe 6.0 will double the data throughput of PCIe 5.0 to 64 Giga transfers per second (GT/s). The bandwidth of an x16 link, which is common for graphics and network cards, is 128 gigabytes per second (GB/s). The PCIe 6.0 link, like previous versions, is full-duplex, meaning it can supply 128 GB/s bandwidth in both directions at the same time.

PCIe has spread well beyond servers and PCs. The application of PCIe is limitless with its economies of scale, making it appealing for data-centric applications in the Internet of Things, automotive, medical, and other fields. As a result, the first PCIe 6.0 installations will focus on applications requiring the most bandwidth, such as AI/ML, HPC, networking, and cloud graphics, all situated in the data centre’s core.

New Features in PCIe6

-

PAM4 Signalling

PCIe 6.0 employs PAM4 signaling (“Pulse Amplitude Modulation with four levels”), which combines two bits per clock cycle with four amplitude levels (00, 01, 10, 11), as opposed to PCIe 5.0 and prior versions, which utilized NRZ modulation with one bit per clock cycle and two amplitude levels (0, 1) which is a massive improvement.

-

Forward Error Correction (FEC)

There are always compromises, and shifting to PAM4 signal encoding has a substantially higher Bit Error Rate (BER) than switching to NRZ. A Forward Error Correction (FEC) technique was implemented to combat the increasing mistake rate. Fortunately, the PCIe 6.0 FEC is light enough not to affect latency. To maintain Link, retry probability below 5×10-6 works hand in hand with a robust CRC (Cyclic Redundancy Check). This new FEC feature aims for a latency increase of less than 2ms.

While PAM4 signalling is more prone to mistakes, given the nature of the modulation mechanism, channel loss is unaffected when compared to PCIe 5.0, hence the reach of PCIe 6.0 signals on a PCB will be the same as PCIe 5.0.

-

FLIT Mode

FLIT mode is introduced in PCIe 6.0, where packets are organized in fixed-size Flow Control Units, as opposed to variable-size Flow Control Units in previous PCIe generations.

FLIT mode is introduced in PCIe 6.0, where packets are organized in fixed-size Flow Control Units instead of variable-size Flow Control Units in previous PCIe generations. FLIT mode was introduced because error correction necessitates the use of fixed-size packets; nevertheless, it also simplifies data handling at the controller level, resulting in improved bandwidth efficiency, lower latency, and a smaller controller footprint. For a moment, consider bandwidth efficiency: with fixed-size packets, packet framing at the Physical Layer is no longer required, resulting in 4-byte savings per packet. FLIT encoding also eliminates prior PCIe standards’ 128B/130B encoding and DLLP (Data Link Layer Packets) overhead, resulting in significantly improved TLP (Transaction Layer Packet) performance, especially for smaller one’s packets.

PCIe is prevalent in current computer systems. Rambus anticipates rapid adoption of PCIe 6.0 in performance-critical applications such as AI/ML, HPC, cloud computing, and networking due to its passive improvements and upgrades when compared to PCIe 5.0.

Thank you! Please share your positive feedback. 🔋

How could we improve this post? Please Help us. 😔

[Senior News Reporter]

Avinash is currently pursuing a Business degree in Australia. For more than 5 years, he has been working as a gaming journalist, utilizing his writing skills and love for gaming to report on the latest updates in the industry. Avinash loves to play action games like Devil May Cry and has also been mentioned on highly regarded websites, such as IGN, GamesRadar, GameRant, Dualshockers, CBR, and Gamespot.