- A new AMD patent wants to introduce a dynamic cache memory cleaning system for processors.

- The system can boost performance by writing dirty cache back to memory during low traffic periods instead of randomly.

- This hardware-level solution could be integrated into future AMD CPUs, enhancing the gaming experience.

Giants like Intel and AMD have continually improved computer processors across various generations, employing different methods. AMD now plans to optimize future Ryzen processors by evolving its cache management system.

We have dug up a new patent by AMD that discusses a dynamic cache management system for processors. It proposes a hardware-level solution that clears the cache during low traffic to prevent slowdowns.

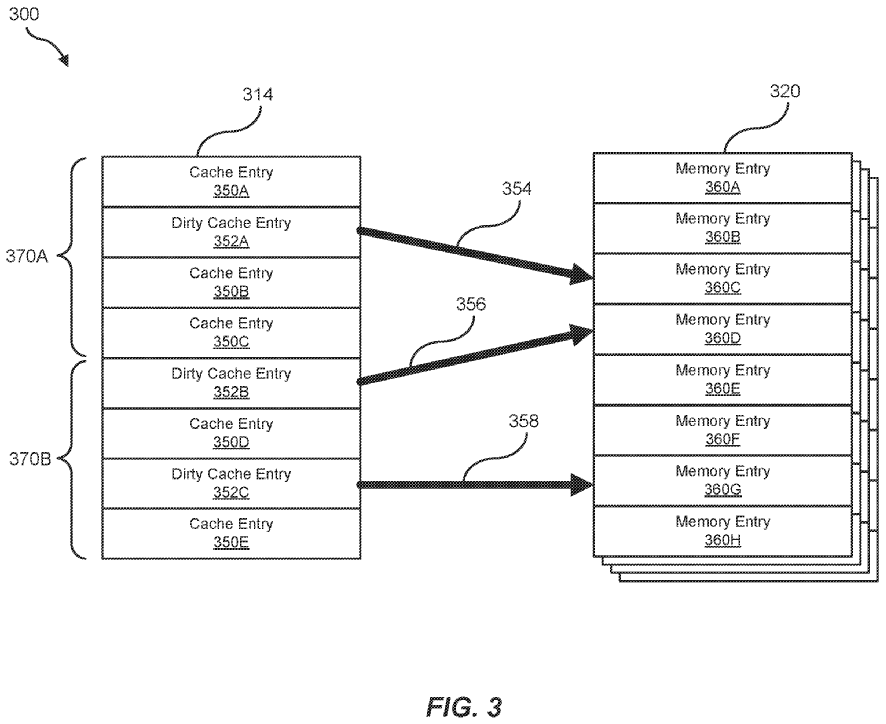

The dirty cache entries can be written back to memory during a low-utilization period, rather than the process being random. This can significantly increase system performance during CPU-intensive tasks, such as gaming, 3D rendering, and similar activities.

[The System] opportunistically perform[s] cache rinsing by writing dirty cache entries from a cache back to memory during a low utilization time period […]. [It] improve[s] the functioning of a computer itself by more efficiently utilizing memory bandwidth and more effectively updating memory coherency, further improving cache performance.

Why it matters: The new dynamic cache management system may prove to be the next big step for consumer-grade processors. We may see it improving the efficiency of future Ryzen processors.

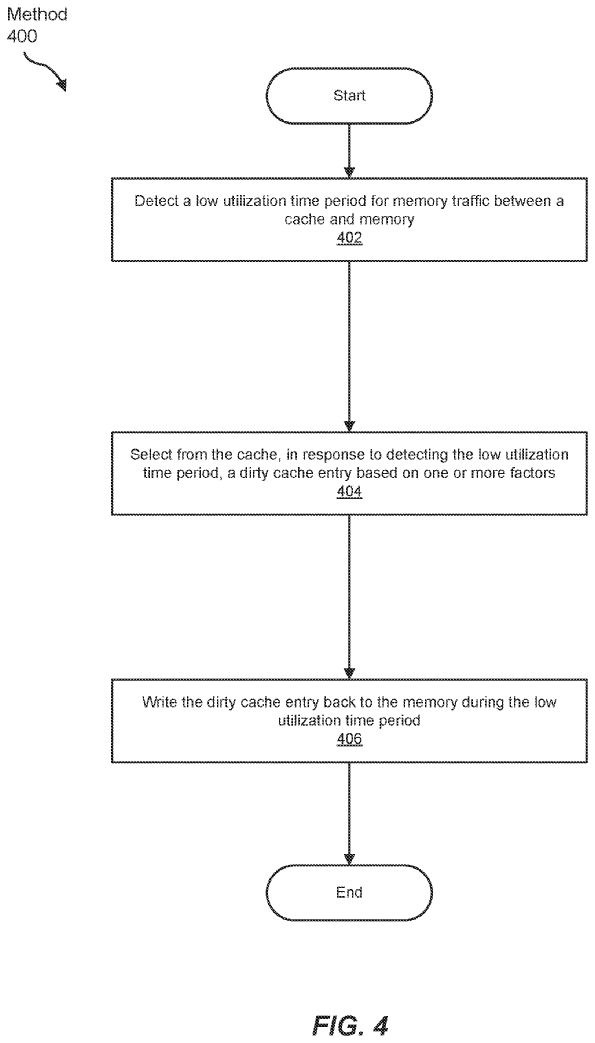

The patent “Dynamically controlled cache rinsing” discusses a concept yet to be applied to consumer-grade processors. The smart cache system monitors bandwidth and clears data only when it won’t cause delays.

These unneeded cache entries are selected based on different criteria to be written back to memory in low traffic periods. AMD argues that cache management is currently entirely random; at worst, the dirty cache is written back to memory when resources are needed.

This impacts performance during peak traffic, but dynamic cache management frees up bandwidth when it’s needed most.

Cache rinsing involves writing dirty cache entries or lines back to memory before the cache entries are evicted for new entries. Because cache rinsing involves writing to memory, cache rinsing can reduce available memory bandwidth particularly if performed at inopportune times.

AMD may implement this opportunistic cache rinsing strategy in its future commercial processor lineup. This system would be a great boon for gamers wanting peak optimization during CPU-heavy AAA gaming.

AMD has published various other unique patents in the past, including one that secures built-in liquid cooling for processors using 3D stacking, and another that discusses saving bricked GPUs after failed VBIOS updates with new software-based recovery.

Do you think AMD will further improve the performance of its consumer-grade processors by bringing a dynamic cache management system? Let us know your thoughts in the comments below, or join the discussion on the Tech4Gamers forum.

Thank you! Please share your positive feedback. 🔋

How could we improve this post? Please Help us. 😔

Shameer Sarfaraz has previously worked for eXputer as a Senior News Writer for several years. Now with Tech4Gamers, he loves to devoutly keep up with the latest gaming and entertainment industries. He has a Bachelor’s Degree in Computer Science and years of experience reporting on games. Besides his passion for breaking news stories, Shahmeer loves spending his leisure time farming away in Stardew Valley. VGC, IGN, GameSpot, Game Rant, TheGamer, GamingBolt, The Verge, NME, Metro, Dot Esports, GameByte, Kotaku Australia, PC Gamer, and more have cited his articles.