- Intel’s future processor, Panther Lake, is expected to be an improvement over Lunar Lake and Arrow Lake.

- A more significant architectural shift is anticipated with Nova Lake, which will introduce a new RingBus design.

- The upcoming Nova Lake architecture is significant as Intel competes with AMD’s forthcoming Zen 6.

We can agree that Intel had many obvious faults indicative of an architecture developed long in advance, which were oddly lessened in Lunar Lake, even if Arrow Lake was a step forward for Intel in many aspects.

The most intriguing item will be what comes next year, but Panther Lake, which is almost ready for launch, will have several upgrades over these two systems. The answers will arrive with Nova Lake, and they mostly entail several fundamental setups built on a recently unveiled new RingBus.

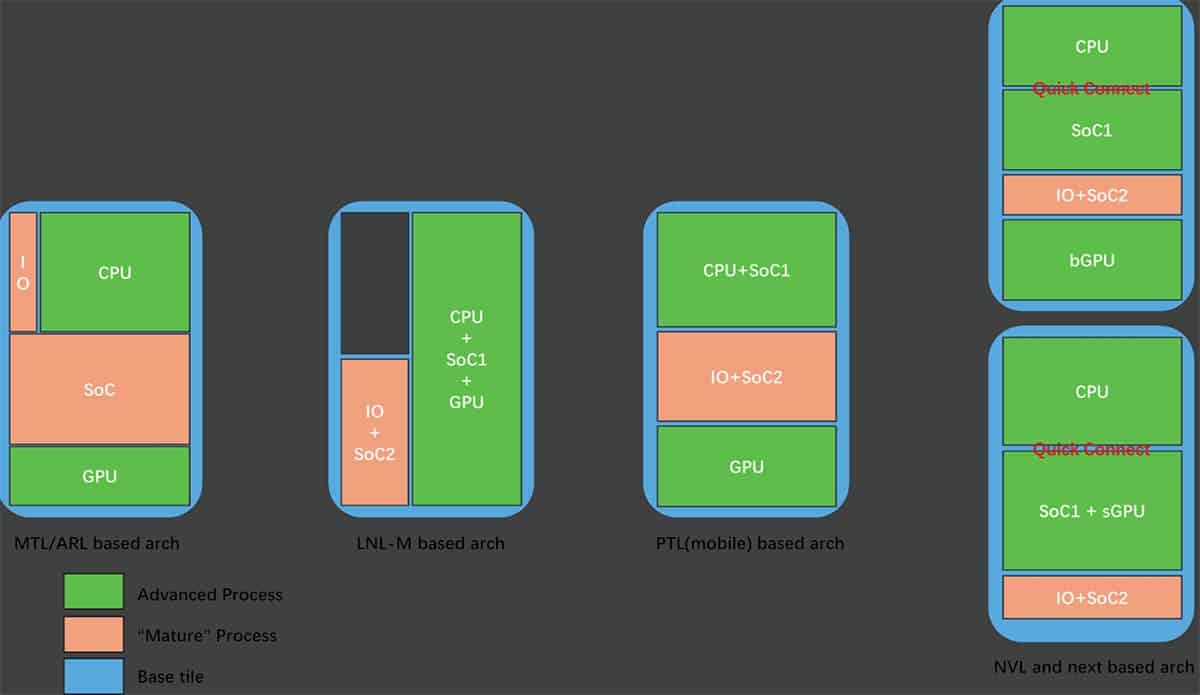

Intel will introduce a series of improvements that, in principle, appear promising. As we already know, there will be two types of CPU configurations, which we’ve summarised on a few occasions and which you’ll have seen in the image above, so we’ll skip that theoretical part and move on to the latest leaks.

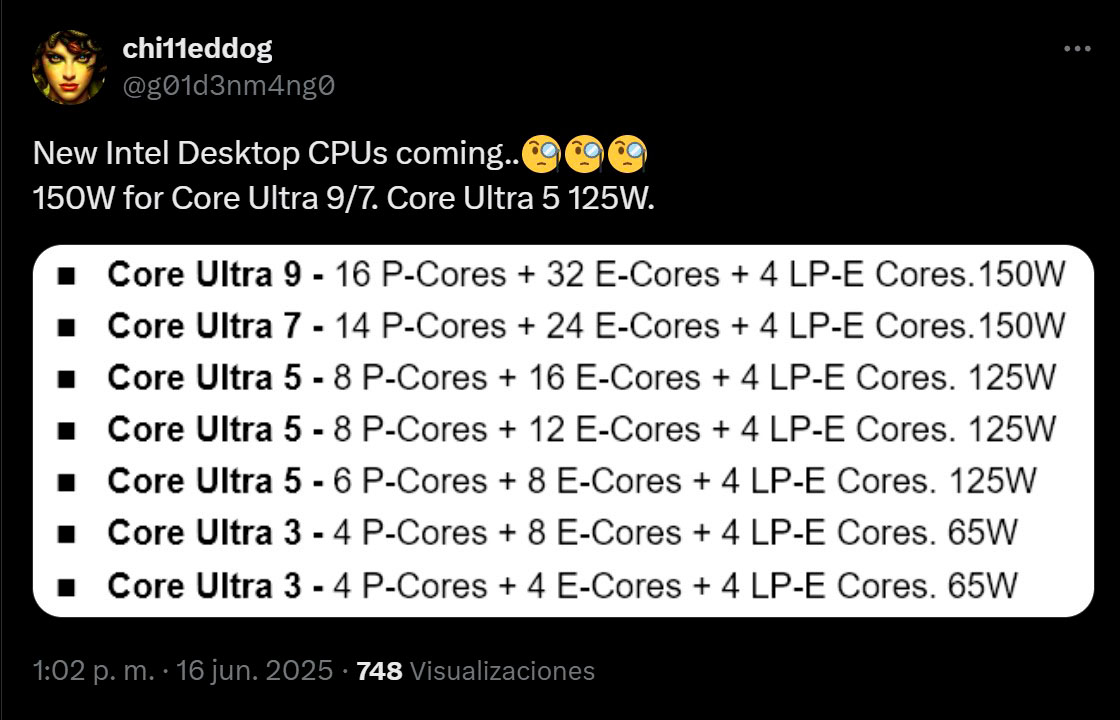

To reduce overall latency, Intel had to overclock the Core Ultra 200S. This is likely to be standard in the next Core Ultra 300S upgrade, which is effectively a palliative rehash with enhanced AI performance, at least, that’s what leaks have suggested.

Given this configuration, Arrow Lake now has the following, taking into consideration the two rows of cores on either side of the Tile, divided by the middle L2 and L3, with “P” denoting the P-cores and “E” denoting the E-cores.

Intel will initially include two P-cores in the CPU Tile arrangement in order to prioritise performance and minimise latency in demanding games. This is something that both core configurations will initially have, as each will have four cores available.

In the first configuration, there will be two clusters of E-Cores in a row, followed by two P-Cores at the end. We insist on having two P-Cores on each side of L2 and L3, so the count is actually twice, even though we are only examining one RingBus row. This is where the variations originate.

In the second configuration, on either side of the CPU tile, the E-Core cluster will appear after the two P-Cores, followed by two additional P-Cores and then another E-Core cluster.

The highest-performance option that separates the Core Ultra 9 from the Core Ultra 7 is the second base tile, as the latency between the P-Cores is shorter than in the original setup, which occurs at the beginning and end of the CPU Tile. The intriguing aspect of this is that, as can be seen in the first slide above, Intel will have up to 8 P-Cores with low latency in CPUs, utilising the two Base Tiles.

To enhance performance in games that require high-performance cores, they would first have 16 E-Cores. After that, one of the Base Tiles would choose to have four P-Cores. Lastly, for games that are highly optimised, the P-Core of the other Base Tile would stay at the end of that CPU Tile.

With its multi-core configurations and potential new RingBus, Nova Lake appears quite promising in light of all of this. However, there is still more work to be done to increase the excitement, as AMD and Intel need to narrow a significant gap, and Zen 6 is rapidly approaching.

Thank you! Please share your positive feedback. 🔋

How could we improve this post? Please Help us. 😔