- A new AMD patent introduces a RAM architecture that boasts data rates twice that of current DDR5.

- The new architecture is designed to overcome the limitations of DDR5, enabling it to keep pace with GPUs and servers.

- It achieves a data rate of 12.8 Gbps on the memory bus, twice the native 6.4 Gbps speeds of the DDR5 chips.

With DDR5 lagging in recent years, data and bandwidth rates have not kept up with the increasing demands of gaming and other industries. However, AMD has stepped in with an easily adaptable solution that pushes RAM in a new direction.

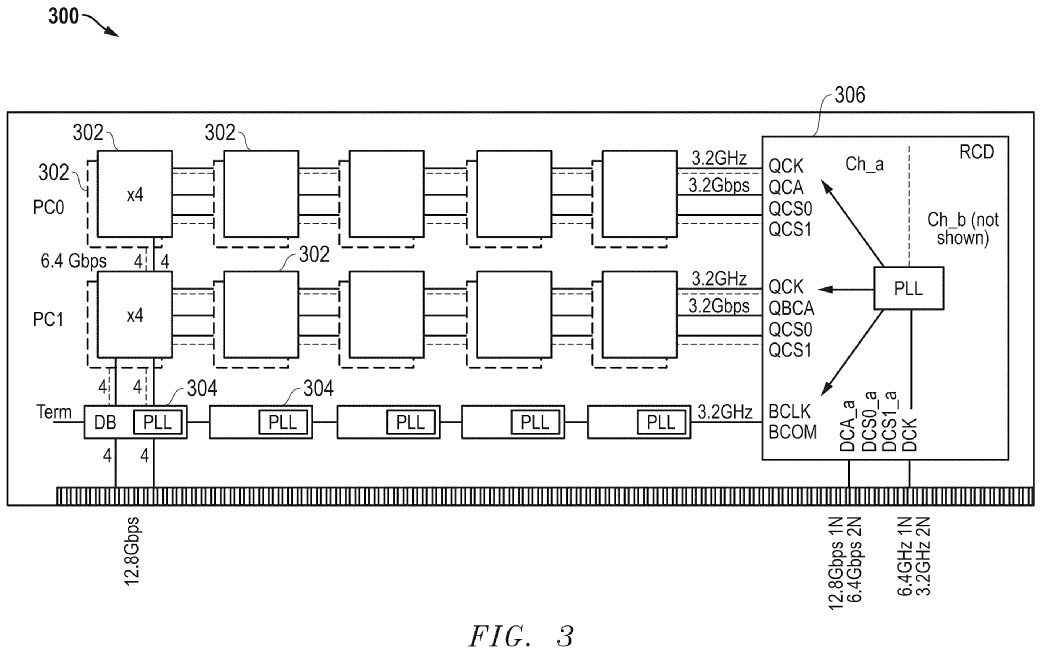

We have found a new AMD patent that discusses an upgrade to DDR5 chip architecture. It describes a high-bandwidth dual inline memory module (HB-DIMM) architecture that boosts memory performance by introducing pseudo channels and intelligent signal routing.

Each HB-DIMM boasts multiple DRAM chips connected to data buffer chips, which transmit data at twice the current speeds. It practically doubles the data rate to 12.8 Gbps on the memory bus, twice the current native 6.4 Gbps speeds.

It achieves this feat without changing the underlying DRAM chips, scaling performance with existing tech to make it widely adaptable.

A high-bandwidth dual-inline memory module (HB-DIMM) is adapted […]. The plurality of data buffer chips are coupled to respective sets of the memory chips and capable of transmitting data from the memory chips over a host bus at a data rate twice that of the memory chips.

Why it matters: AMD’s newly proposed RAM architecture is a direct upgrade to the stagnating DDR5 chips. This could finally provide us with better bandwidth and data speeds necessary for high-end gaming and AI industries.

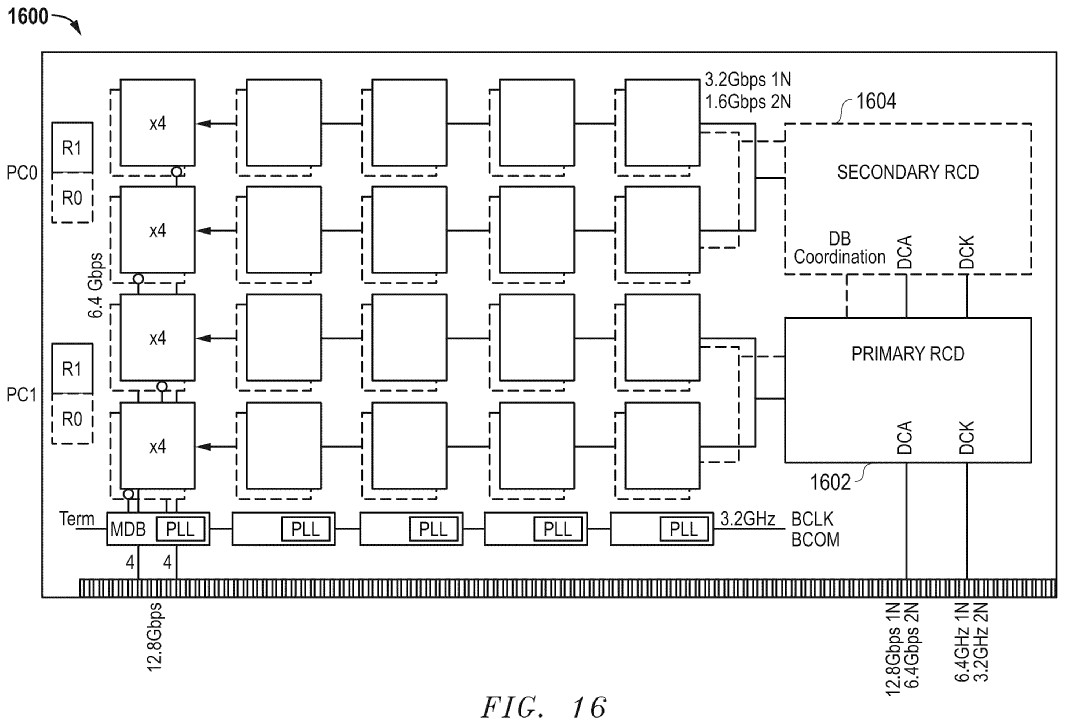

The “HIGH-BANDWIDTH MEMORY MODULE ARCHITECTURE” patent describes a register clock driver (RCD) circuit that decodes memory commands and uses a chip identifier (CID) bit to route command or address signals to independently addressable pseudo-channels. This enables parallel access and improved throughput.

By supporting 1n and 2n operating modes, the architecture boasts flexible clocking and signaling strategies to optimize timing margins and compatibility with DDR5 standards. Data transfer also uses a non-interleaved format to simplify signal integrity and reduce latency.

AMD argues that DDR5 is unable to keep up with the growing memory bandwidth required for high-performance graphics processors and servers.

the memory bandwidth required for applications such as high-performance graphics processors, […] are outpacing the roadmap of bandwidth improvements for DDR DRAM chips. Improved DIMM architectures are needed to meet such requirements with current DDR chip technologies such as DDR5.

Since the new system can be programmed to switch between pseudo-channel and quad-rank configurations, it is adaptable for high-performance computing environments where memory bandwidth is critical.

AMD has published numerous innovative patents in the past, including a new blower fan design aimed at addressing heating issues in gaming laptops, and another that introduces an innovative cache memory cleaning system to boost processor performance significantly.

Do you think the new AMD patent will lead to the next evolution of the RAM architecture? Let us know your thoughts in the comments below, or join the discussion on the Tech4Gamers forum.

Thank you! Please share your positive feedback. 🔋

How could we improve this post? Please Help us. 😔

Shameer Sarfaraz has previously worked for eXputer as a Senior News Writer for several years. Now with Tech4Gamers, he loves to devoutly keep up with the latest gaming and entertainment industries. He has a Bachelor’s Degree in Computer Science and years of experience reporting on games. Besides his passion for breaking news stories, Shahmeer loves spending his leisure time farming away in Stardew Valley. VGC, IGN, GameSpot, Game Rant, TheGamer, GamingBolt, The Verge, NME, Metro, Dot Esports, GameByte, Kotaku Australia, PC Gamer, and more have cited his articles.